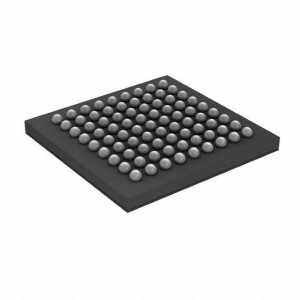

TMS320VC5509AZAY Цифрови сигнални процесори и контролери – DSP, DSC цифров сигнален процесор с фиксирана точка 179-NFBGA -40 до 85

♠ Описание на продукта

| Атрибут на продукта | Стойност на атрибута |

| производител: | Texas Instruments |

| Категория на продукта: | Цифрови сигнални процесори и контролери - DSP, DSC |

| RoHS: | Подробности |

| Продукт: | DSP |

| серия: | TMS320VC5509A |

| Стил на монтаж: | SMD/SMT |

| Опаковка/Калъф: | NFBGA-179 |

| Ядро: | C55x |

| Брой ядра: | 1 ядро |

| Максимална тактова честота: | 200 MHz |

| L1 кеш памет за инструкции: | - |

| L1 кеш памет за данни: | - |

| Размер на програмната памет: | 64 kB |

| Размер на RAM за данни: | 256 kB |

| Работно захранващо напрежение: | 1,6 V |

| Минимална работна температура: | - 40 С |

| Максимална работна температура: | + 85 С |

| Опаковка: | поднос |

| Марка: | Texas Instruments |

| Тип инструкция: | Фиксирана точка |

| Тип интерфейс: | I2C |

| Чувствителен към влага: | да |

| Вид на продукта: | DSP - цифрови сигнални процесори и контролери |

| Фабрично количество в опаковка: | 160 |

| подкатегория: | Вградени процесори и контролери |

| Захранващо напрежение - Макс. | 1,65 V |

| Захранващо напрежение - мин.: | 1,55 V |

| Таймери за наблюдение: | Таймер за наблюдение |

♠ TMS320VC5509A Цифров сигнален процесор с фиксирана точка

Цифровият сигнален процесор (DSP) с фиксирана точка TMS320VC5509A е базиран на ядрото на CPU процесора от поколение TMS320C55x DSP.Архитектурата C55x™ DSP постига висока производителност и ниска мощност чрез увеличен паралелизъм и пълен фокус върху намаляването на разсейването на мощността.Централният процесор поддържа вътрешна шинна структура, която се състои от една програмна шина, три шини за четене на данни, две шини за запис на данни и допълнителни шини, предназначени за периферна и DMA дейност.Тези шини осигуряват възможност за извършване на до три четения на данни и два записа на данни в един цикъл.Успоредно с това DMA контролерът може да извърши до два трансфера на данни на цикъл, независимо от дейността на процесора.

C55x CPU осигурява две единици за умножение-натрупване (MAC), всяка от които може да извършва 17-битово x 17-битово умножение в един цикъл.Централно 40-битово аритметично/логическо устройство (ALU) се поддържа от допълнително 16-битово ALU.Използването на ALU е под контрол на набор от инструкции, осигурявайки възможност за оптимизиране на паралелна дейност и консумация на енергия.Тези ресурси се управляват в модула за адрес (AU) и модула за данни (DU) на C55x CPU.

Генерацията C55x DSP поддържа набор от инструкции с променлива ширина на байта за подобрена плътност на кода.Инструкционният модул (IU) изпълнява 32-битови извличания на програми от вътрешна или външна памет и подрежда инструкции на опашка за програмния модул (PU).Програмният модул декодира инструкциите, насочва задачите към ресурсите на AU и DU и управлява напълно защитения конвейер.Възможността за предсказуемо разклоняване избягва промиването на тръбопровода при изпълнение на условни инструкции.

Функциите за вход и изход с общо предназначение и 10-битовият A/D осигуряват достатъчно щифтове за статус, прекъсвания и битови I/O за LCD дисплеи, клавиатури и медийни интерфейси.Паралелният интерфейс работи в два режима, или като подчинен на микроконтролер, използващ HPI порта, или като паралелен медиен интерфейс, използващ асинхронния EMIF.Серийните носители се поддържат чрез две периферни устройства MultiMedia Card/Secure Digital (MMC/SD) и три McBSP.

Периферният комплект 5509A включва интерфейс за външна памет (EMIF), който осигурява незалепващ достъп до асинхронни памети като EPROM и SRAM, както и до високоскоростни памети с висока плътност като синхронна DRAM.Допълнителните периферни устройства включват универсална серийна шина (USB), часовник в реално време, таймер за наблюдение, I2C мулти-главен и подчинен интерфейс.Три пълнодуплексни многоканални буферирани серийни порта (McBSP) осигуряват незалепващ интерфейс към различни индустриални стандартни серийни устройства и многоканална комуникация с до 128 отделно разрешени канала.Подобреният интерфейс на хост-порт (HPI) е 16-битов паралелен интерфейс, използван за осигуряване на достъп на хост процесора до 32K байта вътрешна памет на 5509A.HPI може да бъде конфигуриран както в мултиплексиран, така и в немултиплексиран режим, за да осигури незалепващ интерфейс към голямо разнообразие от хост процесори.DMA контролерът осигурява движение на данни за шест независими контекста на канала без намеса на процесора, осигурявайки DMA пропускателна способност до две 16-битови думи на цикъл.Включени са също два таймера с общо предназначение, до осем специални I/O пина с общо предназначение (GPIO) и генериране на часовник с цифрова фазово заключена верига (DPLL).

5509A се поддържа от всепризнатата в индустрията eXpressDSP™, интегрирана среда за разработка Code Composer Studio™ (IDE), DSP/BIOS™, стандарт за алгоритъм на Texas Instruments и най-голямата мрежа на трети страни в индустрията.IDE на Code Composer Studio включва инструменти за генериране на код, включително C компилатор и Visual Linker, симулатор, RTDX™, драйвери за емулационни устройства XDS510™ и модули за оценка.5509A се поддържа и от библиотеката C55x DSP, която включва повече от 50 основни софтуерни ядра (FIR филтри, IIR филтри, FFT и различни математически функции), както и библиотеки за поддръжка на чипове и платки.

Ядрото TMS320C55x DSP е създадено с отворена архитектура, която позволява добавянето на специфичен за приложението хардуер за повишаване на производителността на специфични алгоритми.Хардуерните разширения на 5509A постигат перфектния баланс между производителност на фиксирана функция с програмируема гъвкавост, като същевременно постигат ниска консумация на енергия и цена, която традиционно е била трудна за намиране на пазара на видеопроцесори.Разширенията позволяват на 5509A да достави изключителна производителност на видео кодек с повече от половината му честотна лента, достъпна за извършване на допълнителни функции като преобразуване на цветово пространство, операции с потребителски интерфейс, сигурност, TCP/IP, гласово разпознаване и преобразуване на текст в реч.В резултат на това един 5509A DSP може да захранва повечето преносими цифрови видео приложения с излишно пространство за обработка.За повече информация вижте TMS320C55x Hardware Extensions for Image/Video Applications Programmer's Reference (литературен номер SPRU098).За повече информация относно използването на DSP библиотеката за обработка на изображения вижте справочника на програмиста на библиотеката за обработка на изображения/видео TMS320C55x (литературен номер SPRU037).

• Високопроизводителен, нискоенергиен, цифров сигнален процесор TMS320C55x™ с фиксирана точка

− 9.26-, 6.95-, 5-ns Време на цикъл на инструкция

− 108-, 144-, 200-MHz тактова честота

− Една/две инструкции(и), изпълнени на цикъл

− Двойни множители [До 400 милиона умножения-натрупвания за секунда (MMACS)]

− Две аритметични/логически единици (ALU)

− Три вътрешни шини за четене на данни/операнд и две вътрешни шини за запис на данни/операнд

• 128K x 16-битова вградена RAM памет, съставена от:

− 64K байта RAM с двоен достъп (DARAM) 8 блока от 4K × 16-бита

− 192K байта RAM с единичен достъп (SARAM) 24 блока от 4K × 16-бита

• 64K байта ROM в чип с едно състояние на изчакване (32K × 16 бита)

• 8M × 16-битово максимално адресируемо пространство на външната памет (синхронна DRAM)

• 16-битова външна паралелна шина памет, поддържаща или:

− Интерфейс за външна памет (EMIF) с GPIO възможности и Glueless интерфейс за:

− Асинхронна статична RAM (SRAM)

− Асинхронен EPROM

− Синхронна DRAM (SDRAM)

− 16-битов паралелен подобрен хост-порт интерфейс (EHPI) с GPIO възможности

• Програмируемо управление с ниска мощност на шест функционални домейна на устройството

• Логика за емулация, базирана на сканиране в чип

• Вградени периферни устройства

− Два 20-битови таймера

− Таймер за наблюдение

− Шестканален контролер за директен достъп до паметта (DMA).

− Три серийни порта, поддържащи комбинация от:

− До 3 многоканални буферирани серийни порта (McBSP)

− До 2 интерфейса за мултимедия/сигурна цифрова карта

− Програмируем часовников генератор на фазово заключена верига

− Седем (LQFP) или осем (BGA) I/O пина с общо предназначение (GPIO) и изходен щифт с общо предназначение (XF)

− USB пълноскоростен (12 Mbps) подчинен порт, поддържащ групови, прекъсващи и изохронни трансфери

− Inter-Integrated Circuit (I2C) Multi-Master и Slave интерфейс

−Часовник в реално време (RTC) с кристален вход, отделен домейн на часовника, отделно захранване

− 4-канален (BGA) или 2-канал (LQFP) 10-битов последователен A/D

• IEEE Std 1149.1† (JTAG) логика на гранично сканиране

• Пакети:

− 144-терминален нисък профил Quad Flatpack (LQFP) (PGE суфикс)

− 179-Terminal MicroStar BGA™ (Ball Grid Array) (GHH суфикс)

− 179-терминален безоловен MicroStar BGA™ (матрица с топка) (суфикс ZHH)

• 1.2-V Core (108 MHz), 2.7-V – 3.6-VI/Os

• 1.35-V Core (144 MHz), 2.7-V – 3.6-VI/Os

• 1.6-V Core (200 MHz), 2.7-V – 3.6-VI/Os

• Хибридна, електрическа и задвижваща система (EV/HEV)

– Система за управление на батерията (BMS)

– Вградено зарядно устройство

– Тягов инвертор

– DC/DC преобразувател

– Стартер/генератор